# MITSUBISHI

# SAFETY PRECAUTIONS ●

(Read these precautions before using.)

When using Mitsubishi equipment, thoroughly read this manual and the associated manuals introduced in this manual. Also pay careful attention to safety and handle the module properly.

These precautions apply only to Mitsubishi equipment. Refer to the CPU module user's manual for a descriprion of the PC system safty precautions.

These ● **SAFETY PRECAUTIONS** ● classifive the safty precautions into two categories: "DANGER" and "CAUTION".

Depending on circumestances, procedures indicated by A CAUTION may also be linked to serious results.

In many case, it is important to follow the directions for usage.

Store this manual in a safe place so that you can take it out and read it whenever necessary. Always forward it to the end user.

[System Design Precautions]

#### [System Design Precautions]

[Cautions on Mounting]

[Cautions on Wiring]

[Cautions on Wiring]

[Cautions on Startup and Maintenance]

DANGER

- Before starting cleaning or terminal screw retightening, be sure to switch power off externally in all phases. Failure to do so can cause an electric shock.

- CAUTION

Do not disassemble or modify any module. This will cause failure, malfunction, injuries, or fire.

Be sure to install or remove the module after switching power off externally in all phases. Failure to do so can cause the module to fail or malfunction. Undertightening of screws can cause the module to fail, short, or malfunction. Overtightening can damage the screws and module, causing the module to fail, short or malfunction.

When replacing fuses, be sure to use the prescribed fuse. A fuse of the wrong capacity could cause a fire.

Before touching the module, be sure to touch ground metal or similar material to discharge static electricity from human body, etc. Failure to do so can cause the module to fail or malfunction.

[Cautions on Disposal]

| • | Dispose of this product as industrial waste. |  |

|---|----------------------------------------------|--|

# CAUTION

# MITSUBISHI PROGRAMMABLE CONTROLLER A0J2-D61S1 HIGH-SPEED COUNTER MODULE

On A0J2-D61S1, the count ratios of input pulses are as described below:

(1) Twice for 1-phase input (2 counts are made for 1 pulse input).

(2) Four times for 2-phase input (4 counts are made for 1 pulse input).

For further details, refer to Section 2.2.2 (6) "Counter mode" of the A0J2-D61S1 High-Speed Counter Module User's Manual.

## REVISIONS

# \*The manual number is given on the bottom left of the back cover.

| Print Date | *Manual Number  | Revision                                                                                                                                                                                                             |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nov., 1986 | IB (NA) 66094-A | First edition                                                                                                                                                                                                        |

| Dec., 1988 | IB (NA) 66094-B | Correction<br>Page 2-1, 2-13, 6-6, 6-13, APP-5, APP-6<br>"Instructions for Strategic Materials" added                                                                                                                |

| Dec., 2003 | IB (NA) 66094-C | Partial Correction<br>CONTENTS, Section 2.2.2, 2.5, 3.1, 4.1.2, 6.1, 6.2, 6.3.1,<br>Appendix 1<br>Partial Addition<br>Section 2.2.2, 2.5, 4.1.2, 6, 6.1, 6.2, Appendix 1<br>Addition<br>SAFETY PRECAUTIONS, WARRANTY |

|            |                 |                                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                                      |

|            |                 | ·                                                                                                                                                                                                                    |

|            | · · ·           |                                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                                      |

|            |                 |                                                                                                                                                                                                                      |

ι.

Japanese Manual Version IB-68007-H

#### INTRODUCTION

Thank you for choosing the Mitsubishi MELSEC-A Series of General Purpose Programmable Controllers. Please read this manual carefully so that the equipment is used to its optimum. A copy of this manual should be forwarded to the end User.

#### CONTENTS

| 1.  | GENERAL DESCRIPTION                                                             |

|-----|---------------------------------------------------------------------------------|

| 2.  | <b>SPECIFICATIONS</b>                                                           |

| 2.1 | General Specifications                                                          |

| 2.2 | 2.2.1 Performance list                                                          |

|     | 2.2.2 Functions                                                                 |

| 2.3 | I/O Signals To and From Programmable Controller CPU                             |

| 2.4 |                                                                                 |

| 2.5 | Interface with External Equipment2-13                                           |

| 3.  | HANDLING                                                                        |

| 3.1 | Handling Instructions                                                           |

| 3.2 |                                                                                 |

| 3.3 |                                                                                 |

| 3.4 |                                                                                 |

|     | 3.4.1 Unit number setting                                                       |

|     | 3.4.2 Ring counter function setting                                             |

|     | 3.4.3 Unit internal power supply (5V DC) setting                                |

|     | 3.4.4 Unit internal power supply (5V DC) check                                  |

| 4.  | WIRING AND INSTALLATION                                                         |

|     |                                                                                 |

| 4.1 | Wiring                                                                          |

|     |                                                                                 |

|     | 4.1.2 Unit wiring examples                                                      |

| 5.  | CONCEPT OF THE D61S1 I/O NUMBERS IN A0J2 SYSTEM $\ldots \ldots 5$ -1 $\sim$ 5-2 |

| 5.1 | I/O Number Assignment and Concept                                               |

| 5.2 | Concept of Parallel I/O Assignment for Use with Remote Station                  |

| 6.  | PROGRAMMING                                                                     |

| 6.1 | General Description of Programming                                              |

| 6.2 |                                                                                 |

| 6.3 |                                                                                 |

|     | 6.3.1 Programming instructions                                                  |

|     | 6.3.2 Basic programs for read and write                                         |

|     | 6.3.3 Program example                                                           |

| 7.  | TEST OPERATION                                                   |

|-----|------------------------------------------------------------------|

| 7.1 | Pre-test Checks                                                  |

| 8.  | TROUBLESHOOTING                                                  |

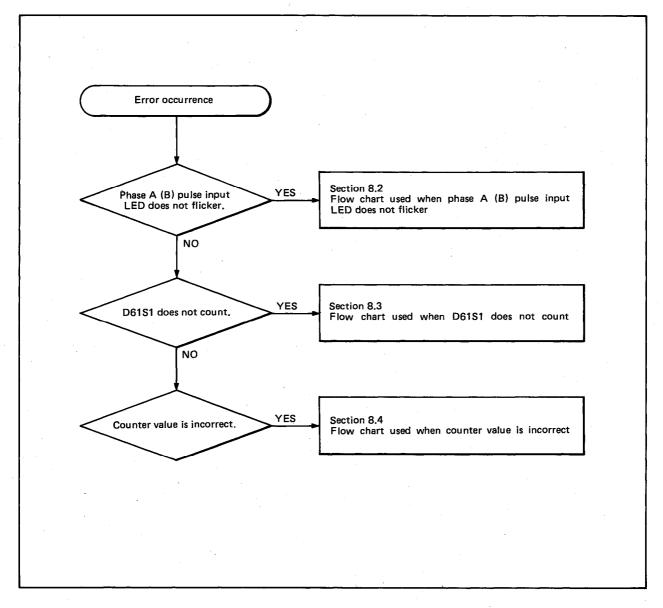

| 8.1 | General Troubleshooting Flow Chart                               |

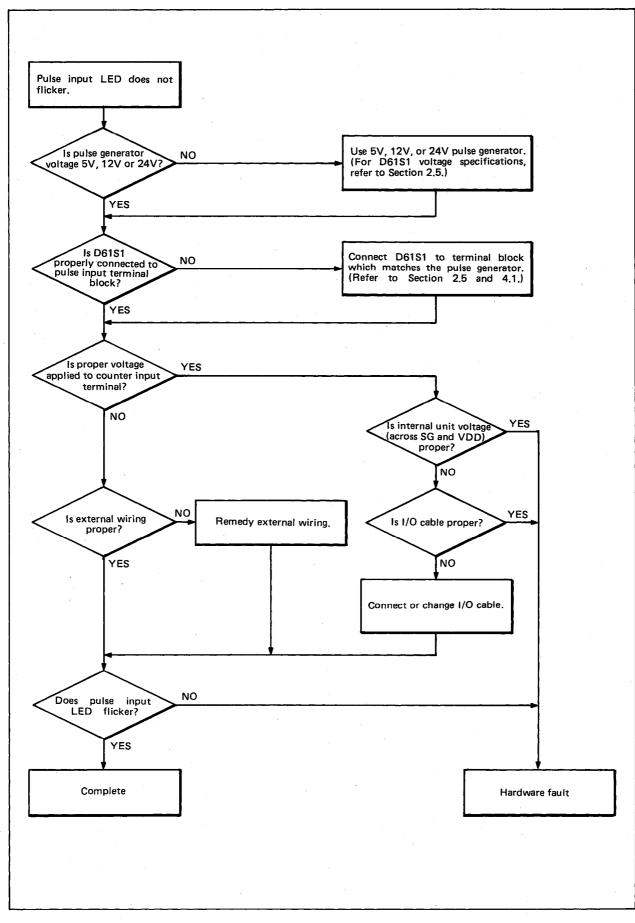

| 8.2 | Flow Chart Used When Phase A(B) Pulse Input LED Does Not Flicker |

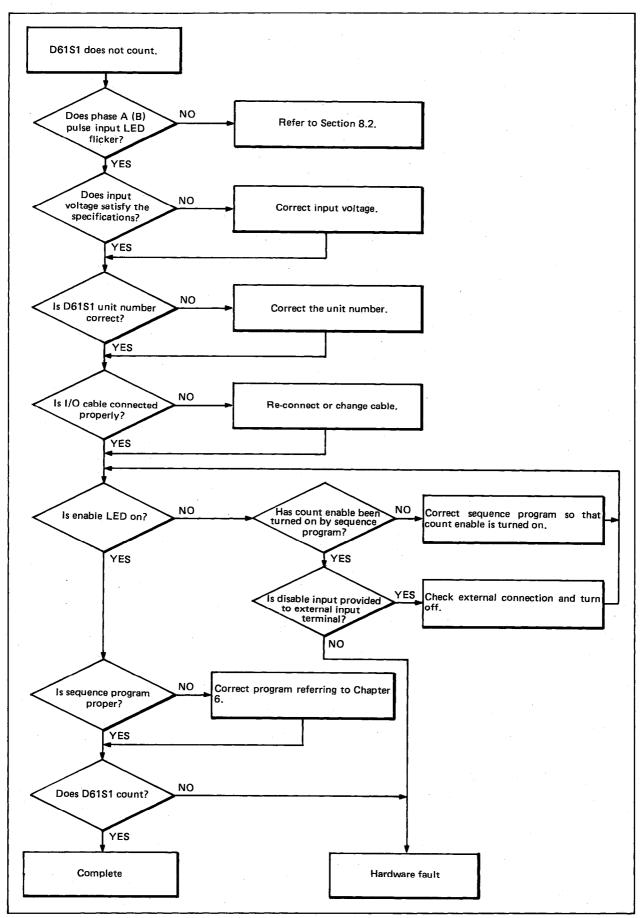

| 8.3 | Flow Chart Used When D61S1 Does Not Count                        |

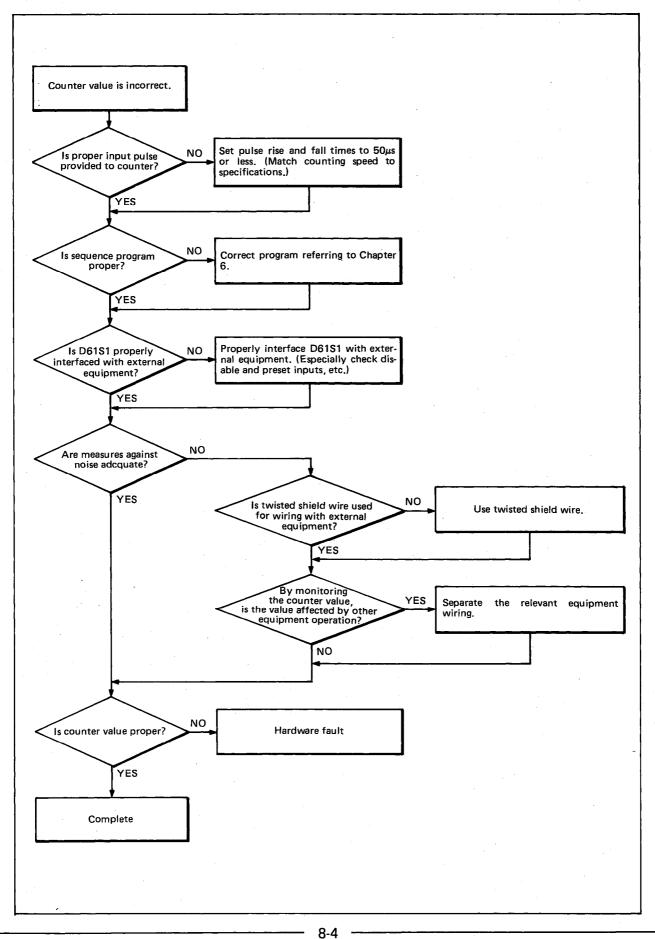

| 8.4 | Flow Chart When Counter Value Is Incorrect                       |

| AP  | PENDICESAPP-1 ~ APP-13                                           |

| AP  | PENDIX 1 Application Circuit Examples                            |

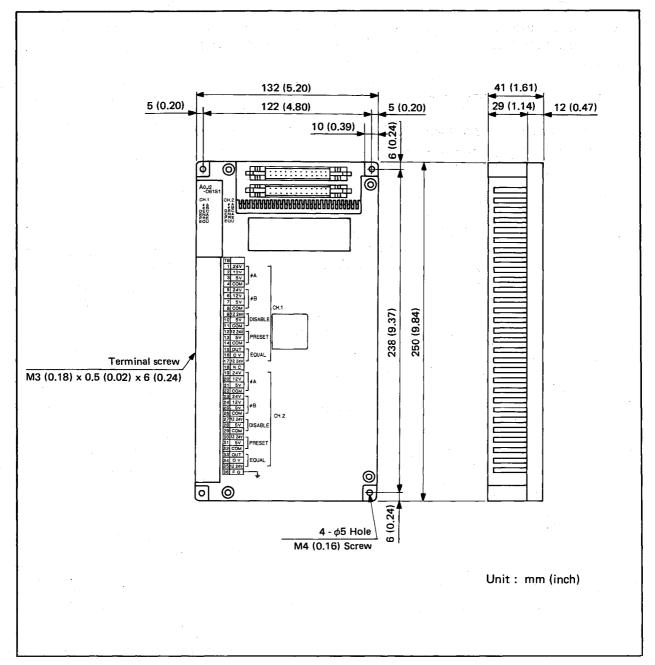

| AP  | PENDIX 2 External ViewAPP-13                                     |

#### 1. GENERAL DESCRIPTION

This User's Manual describes the A0J2-D61S1 high speed counter module (referred to as "D61S1") giving handling instructions and basic programming information. The D61S1 is used in conjunction with MELSEC-A series programmable controllers.

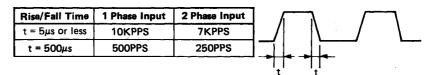

The D61S1 has 1-phase/2-phase input for two channels and allows counting at maximum 10K/7KPPS.

The following manuals may also be required:

A0J2 User's Manual (CPU unit edition) A0J2 User's Manual (I/O unit edition) A0J2CPU Programming Manual A0J2 Data Link System User's Manual

## POINT

In this manual, the D61S1 I/O assignment numbers assume that the unit number is set to 0. If the unit number is other than 0, determine the D61S1 assignment numbers according to the I/O assignment procedure in the Programming Manual.

1-1

This chapter describes the general specifications and performance specifications of the D61S1.

#### **2.1 General Specifications**

The general specifications of D61S1 are shown in Table 2.1.

| · · · · · · · · · · · · · · · · · · · |                                                                                                               |               |               |              |                    |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------|---------------|--------------|--------------------|--|

| ltem                                  | Specifications                                                                                                |               |               |              |                    |  |

| Operating ambient temperature         | 0 to 55°C                                                                                                     |               |               |              |                    |  |

| Storage ambient<br>temperature        |                                                                                                               |               | -20 to 75     | 5°C          |                    |  |

| Operating ambient<br>humidity         |                                                                                                               | 10 to         | 90%RH, no c   | condensatior | ۱<br>              |  |

| Storage ambient<br>humidity           |                                                                                                               | 10 to         | 90%RH, no c   | condensation | 1                  |  |

|                                       | Conforms                                                                                                      | Frequency     | Acceleration  | Amplitude    | Sweep Count        |  |

| Vibration<br>resistance               | to<br>JIS C 0911                                                                                              | 10 to 55Hz    | -             | 0.075mm      | 10 times           |  |

|                                       |                                                                                                               | 55 to 150Hz   | 1G            | -            | *(1 octave/minute) |  |

| Shock resistance                      | Cor                                                                                                           | nforms to JIS | C 0912 (10g > | 3 times in 3 | 3 directions)      |  |

| Noise durability                      | By noise simulator 1500Vpp noise voltage,<br>1µs noise width and 25 to 60Hz noise frequency                   |               |               |              |                    |  |

| Dielectric<br>withstand voltage       | 1500V AC for 1 minute acorss AC external terminals<br>and ground                                              |               |               |              |                    |  |

| Insulation resistance                 | $5M\Omega$ or larger by 500V DC insulation resistance tester across batch of AC external terminals and ground |               |               |              |                    |  |

| Operating<br>ambience                 | Free of corrosive gases. Dust should be minimal.                                                              |               |               |              |                    |  |

| Cooling method                        | Self-cooling                                                                                                  |               |               |              |                    |  |

Table 2.1 General Specifications

#### REMARKS

One octave marked \* indicates a change from the initial frequency to double or half frequency. For example, any of the changes from 10Hz to 20Hz, from 20Hz to 40Hz, from 40Hz to 20Hz, and 20Hz to 10Hz are referred to as one octave.

#### 2.2 Performance Specifications

The D61S1 is used to count pulses which are occuring at a frequency too high for the CPU counters to use. The D61S1 counts independently of the CPU.

#### 2.2.1 Performance list

|                                         | Itom                                   |                                                                                                           | Specifications                                                                |  |  |

|-----------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

|                                         | ltem                                   | -<br>-                                                                                                    | D61S1                                                                         |  |  |

|                                         | 1/O poi                                | nts                                                                                                       | 64 points                                                                     |  |  |

|                                         | Number of c                            | channels                                                                                                  | 2 channels                                                                    |  |  |

|                                         |                                        | Phase                                                                                                     | 1 phase input, 2 phase input                                                  |  |  |

|                                         | Count input<br>signal                  | Signal level<br>(Phase A, Phase B)                                                                        | 5V DC<br>12V DC<br>24V DC<br>24V DC                                           |  |  |

|                                         |                                        | Counting speed<br>*(Maximum)                                                                              | 1 phase input: 10KPPS<br>2 phase input: 7KPPS                                 |  |  |

| -                                       |                                        | Counting range                                                                                            | 24 bits binary<br>0 to 16,777,215 (decimal)                                   |  |  |

| anne                                    |                                        | Form                                                                                                      | Up/down preset counter plus ring counter function                             |  |  |

| Performance specifications of 1 channel | Counter                                | Minimum count<br>pulse width<br>(Set input rise and<br>fall times to<br>5µs. or less.<br>Duty ratio: 50%) | 100µsec<br>142µsec<br>50µsec 50µsec<br>(1 phase input) (2 phase input)        |  |  |

| form                                    | Magnitude                              | Comparison range                                                                                          | 24 bits, binary                                                               |  |  |

| Per                                     | comparison<br>between CPU<br>and D61S1 | Comparison result                                                                                         | Set value < count value<br>Set value = count value<br>Set value > count value |  |  |

|                                         | P                                      | Preset                                                                                                    | 12/24V DC, 3/6mA<br>5V DC, 5mA                                                |  |  |

|                                         | External input                         | Count disable                                                                                             | 12/24V DC, 3/6mA<br>5V DC, 5mA                                                |  |  |

|                                         | External output Coincidence output     |                                                                                                           | Transistor (open collector) output<br>12/24V DC, 0.5A                         |  |  |

|                                         | Current con                            | sumption                                                                                                  | 5V DC, 0.1A                                                                   |  |  |

|                                         | Weig                                   | ht                                                                                                        | 0.65kg                                                                        |  |  |

#### Table 2.2 Performance List

\*: Counting speed is influenced by pulse rise time and fall time. Countable speeds are as follows.

If the rise or fall time is more than  $500\mu s$ , miscount may occur. Use the D61S1 at  $500\mu s$  or less.

MELSEC-

#### 2.2.2 Functions

This section explains the functions of the D61S1.

(1) General description

The D61S1 unit counts high-speed pulse input which cannot be used directly of programmable controller CPU.

D61S1 incorporates a BIN (binary) 24-bit preset counter function which is capable of up/down count, a ring counter function, an internal preset function, an external disable function, a comparison function with BIN 24-bit set value, and a coincidence signal external output function, applicable to two channels.

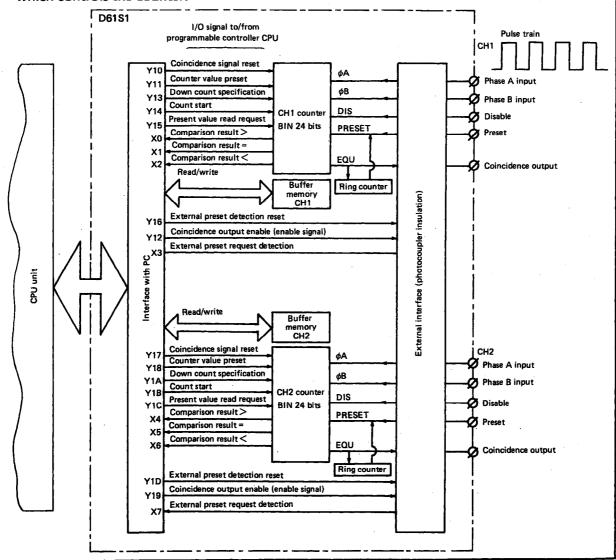

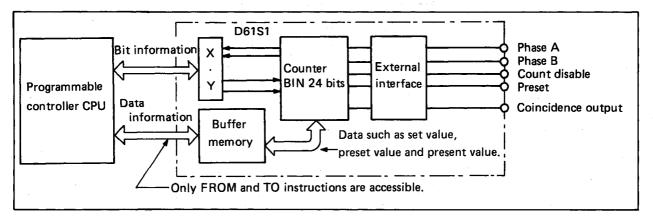

#### (2) Block diagram

The following shows the block diagram of the D61S1.

#### General operation

CH1 counter counts the pulse train entering its phase A input up or down as appropriate. In order to read a count value from the CPU unit, it is necessary to read the value via the buffer memory. I/O signals to and from the programmable controller CPU are used to control the operation of the counter. The buffer memory is used to store set data, etc. which controls the counter.

Fig. 2.1 Block Diagram

#### (3) General description

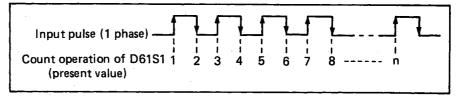

The D61S1 counts the number of input pulses. In the following figure, for example, each time a pulse is input, the D61S1 counts pulses in order of 1 to 2 to 3 to 4 to n. The D61S1 high-speed counter is capable of accepting an input pulse speed of 10KPPS (7KPPS for 2 phases). The allowable counting range is 0 to 16,777,215. The D61S1 unit always executes the comparison function (>, =, <) with a set value (a target value optionally set by user).

(4) Pulse input

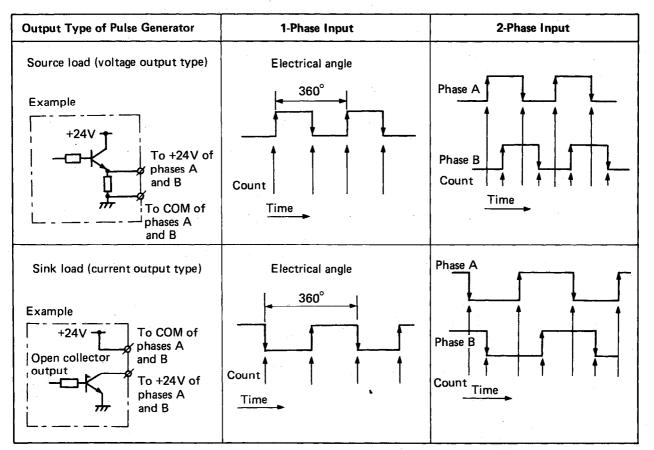

Pulse inputs may be 1-phase or 2-phase. For 1-phase pulse input, up count (down count specification is also possible from the main program) is made each time a pulse is input. For 2-phase pulse input, the up/down direction of the counter is automatically judged depending on the relation between phase A and phase B. In the following figure, the voltages at the D61S1 count input terminal are shown for 1-phase and 2-phase inputs. In this manual, explanation will be given in reference to source load.

Fig. 2.2 1-Phase and 2-Phase Inputs

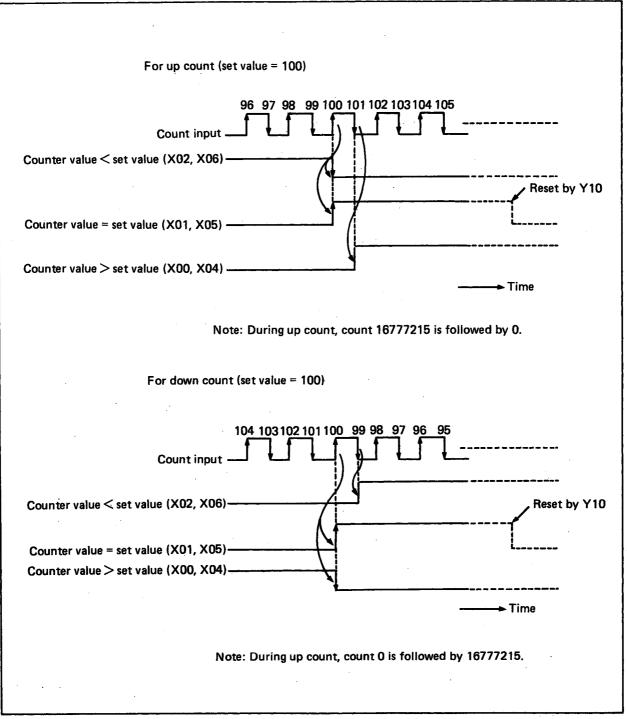

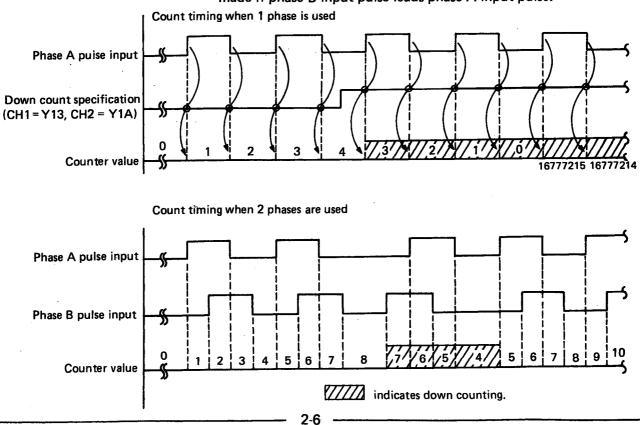

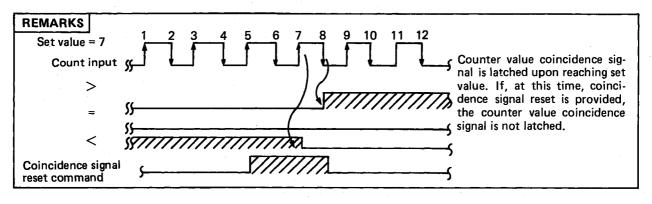

#### (5) Count timing

The timing (for 1 phase input) of the comparison result between a present value and a set value is as indicated below. (Indicated by the assignment numbers of CH1 and 2.)

#### Fig. 2.3 Count Timing

(6) Count mode

On D61S1, the count rations of input pulses are as described below:

- 1) Twice for 1-phase input (2 counts are made for 1 pulse input).

- 2) Four times for 2-phase input (4 counts are made for 1 pulse input).

# POINT

- 1. Each input pulse registers two counts for 1-phase input and four counts for 2-phase input. If the counting range is large, select the pulse generator so that a value twice (for 1 phase) or four times (for 2 phases) greater than the number of generated pulses is within the counting range (0 to 16,777,215).

- 2. For 1-phase input, specify any set value as twice the actual number of input pulses or halve the present value (by using D/instruction). For 2-phase input, specify any set value as four times the actual number of input pulses or divide the present value by four (by using D/instruction).

Counting methods for 1-phase input and 2-phase input are shown below. When 1 phase is used, down counting is made if down count specification is on. When 2 phases are used, down count is made if phase B input pulse leads phase A input pulse.

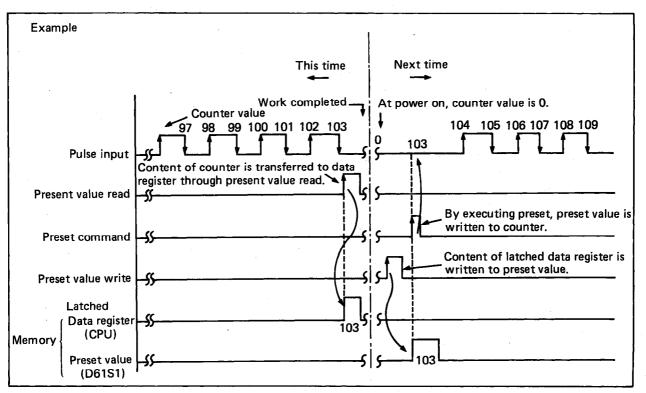

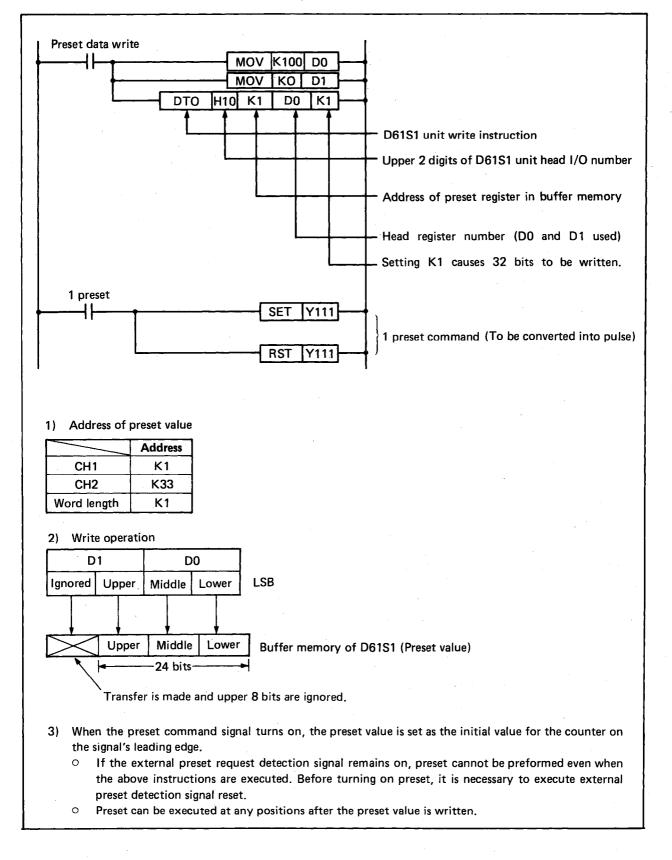

#### (7) Preset function

When the power to the D61S1 is turned off, or the CPU reset, the D61S1 memory contents are lost (i.e. present values, set values etc.). If these values need to be retained for subsequent use, they must be stored in a suitable data register in the Programmable controller CPU.

Fig. 2.4 Preset Operation

The preset value is written to the appropriate buffer memory address (address 1 for CH1, address 33 for CH2) as a 24 bit binary number.

To load the preset value into the counter current value turn on the preset command (Y 11 for CH1, Y18 for CH2) from the programmable controller CPU.

• The preset command may either be loaded from the program or input by applying a voltage to the PRST terminal on the external terminal block (external preset).

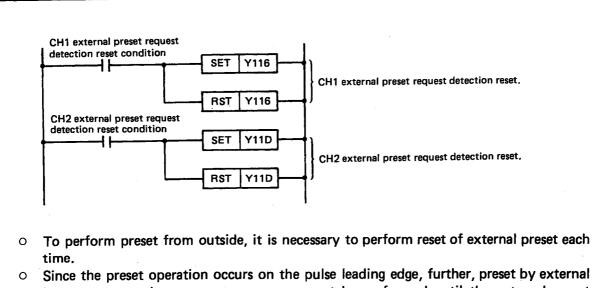

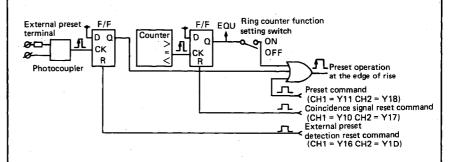

When the external preset signal is given, a flip flop (F/F) is set. If the external preset input turns on again while the F/F is set, the presetting function is stopped. Reset the F/F from the program. (Y16 for CH1, Y1D for CH2) Even if the external preset input remains on, the F/F can be reset. (The F/F is set on the leading edge of the external preset pulse.)

(8) Disable function

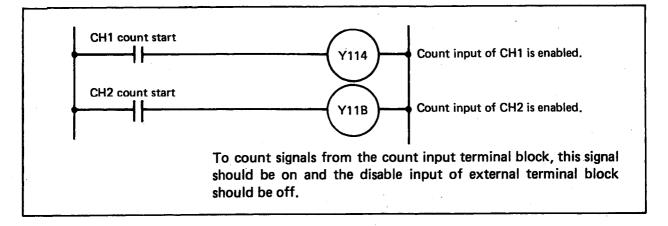

By turning on the count enable signal (i.e. a programmable controller I/O signal), D61S1 starts counting. (Y14 for CH1, Y1B for CH2)

When a voltage is applied to the DIS (disable) terminal on the external input terminal block, the D61S1 stops counting. By utilizing this, counting may be started and stopped by the external input, irrespective of scan time.

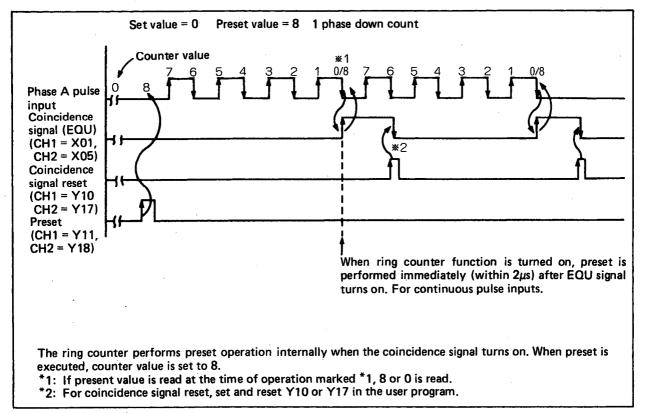

(9) Ring counter function

By setting the ring counter setting switch on the D61S1 circuit board to ON position, automatic preset is performed if the counter value becomes equal to the set value. Use this function for cyclic control such as sizing feed. The timing for the ring counter is shown below.

Fig. 2.5 Ring Counter Operation

(10) External output

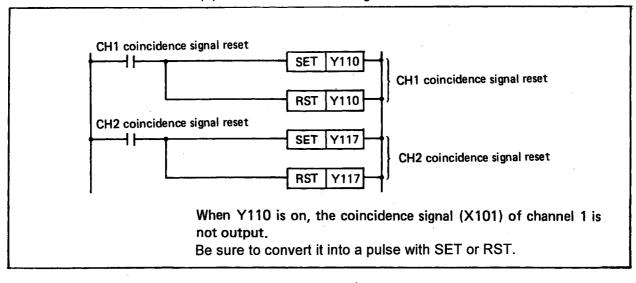

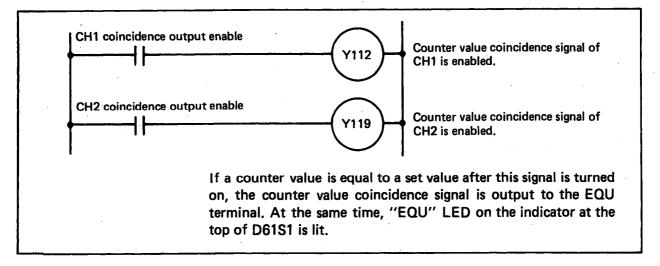

D61S1 is capable of giving a counter value coincidence signal (open collector output) (which turns on if the counter value is equal to the set value). In order to use the counter coincidence signal, it is necessary to turn on the coincidence signal output enable (Y12 for CH1, Y19 for CH2) which is assigned to the programmable controller I/O.

#### 2.3 I/O Signals To and From Programmable Controller CPU

This section describes I/O signals to and from programmable controller CPU when the D61S1 unit number is set to 0.

| CH1 CH2 Signal |                                              | Signal                    | Description               |                                                                                                                               |  |  |  |

|----------------|----------------------------------------------|---------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Γ              | X00 X04 Counter value greater                |                           |                           | Turned on if counter value is greater than set value.                                                                         |  |  |  |

| signal         | X01                                          | X05                       | Counter value coincidence | Latched on if counter value is equal to set value,<br>Turned off by coincidence signal reset command.                         |  |  |  |

| nput           | X02                                          | 02 X06 Counter value less |                           | Turned on if counter value is less than set value.                                                                            |  |  |  |

| <u> </u>       | X03 X07 External preset<br>request detection |                           |                           | Latched on when preset request is given from<br>external input. Turned off when external preset<br>detection signal is reset. |  |  |  |

#### Table 2.3 Input Signals

- Do not use X08 to X0F signals.

- Counter value coincidence signal is turned on when the power is turned on or reset is executed because both the counter value and set value are 0. Therefore, always reset the counter coincidence signal first by turning the coincidence signal reset command on and then off.

- If the counter and set values are still the same after executing the coincidence signal reset command, the counter value coincidence signal is enabled again.

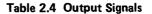

|            | Channel |     | Signal                                        | Operation | Description                                                                                           |  |  |

|------------|---------|-----|-----------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------|--|--|

|            | CH1     | CH2 | Signal                                        | Ťiming    | Description                                                                                           |  |  |

|            | Y10     | Y17 | Coincidence signal<br>reset command           |           | Reset signal for counter value coin-<br>cidence signal (latch) and coincidence<br>output (EQU) signal |  |  |

|            | Y11     | Y18 | Preset command                                | <u>J</u>  | Preset value write execution signal                                                                   |  |  |

| nal        | Y12     | Y19 | Coincidence signal<br>output enable           |           | By turning on this signal, counter value coincidence signal is output to outside.                     |  |  |

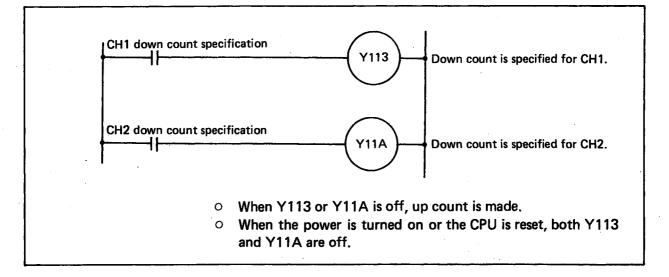

| out signal | Y13     | Y1A | Down count<br>command                         |           | If this signal is on in 1 phase mode, down count is performed.                                        |  |  |

| Output     | Y14     | Y1B | Count enable                                  |           | By turning on this signal, count oper-<br>ation is enabled.                                           |  |  |

|            | Y15     | Y1C | Present value read<br>request                 |           | At the rise of this signal, count value is read as present value.                                     |  |  |

|            | Y16     | Y1D | External preset<br>detection reset<br>command |           | Reset signal of external preset re-<br>quest detection signal (latch)                                 |  |  |

#### IMPORTANT

Y00 to 0F and Y1E to 1F may not be used as they are reserved. If one of the above signals is used (turned on/off) in a sequence program, the functions of the D61S1 cannot be graranteed. However, when the D61S1 is used for remote I/O, Y0E and Y0F may be reset from the program. (For details, refer to Section 6.3.)

2-9

- In Table 2.4 the symbol \_\_\_\_\_\_ indicates that the function is executed on the rise of the signal.

- The coincidence signal latches itself on and must be reset from the sequence program.

The external preset detection reset command must be executed at high speed so that the scan time of the program has mininal effect on the D61S1 operation.

For this reason use a SET Y16 instruction followed by RST Y16, this is fully explained later in this manual.

#### 2.4 Buffer Memory

(1) General description

By using FROM and TO instructions, the D61S1 is capable of making data communication with the programmable controller CPU through the buffer memory.

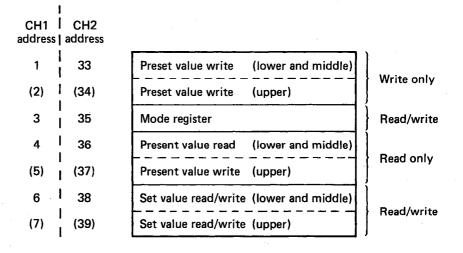

#### (2) Memory map

The memory map inside the buffer memory is shown below. When the power is turned on or the CPU is reset, the contents of the buffer memory are initialized to 0. Preset value, present value, and set value are handled as 24 bit binary. (The address consists of 16 bits and expressed in decimal.)

Addresses in parentheses in the above table indicate those of the upper 8 bits of 24-bit data.

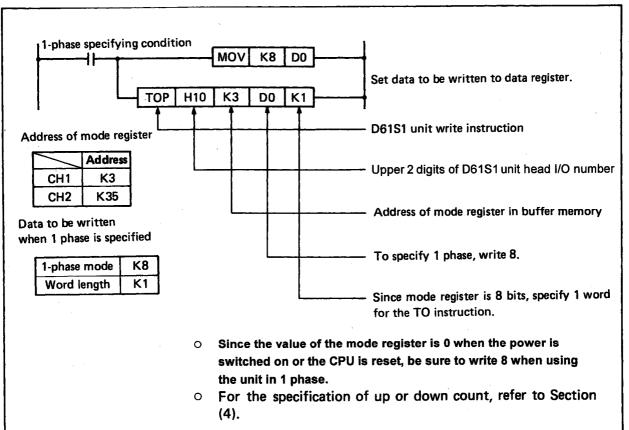

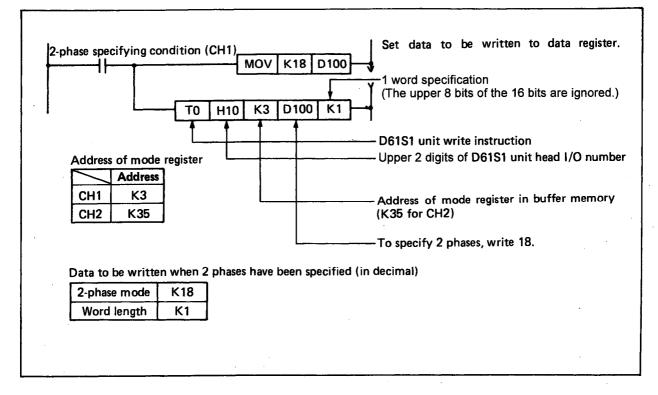

## (3) Setting of mode register

Set the value of the mode register as indicated in the following table. The value is indicated in decimal. When the power is turned on, the value is 0.

| Division of Phase | Data to Be Written |

|-------------------|--------------------|

| 1 phase           | 8                  |

| 2 phases          | 18                 |

### 2.5 Interface with External Equipment

The external equipment interface list of D61S1 is indicated below.

| 1/0      | Internal Circuit                        | Terminal<br>Number |     | Signal                         | Operation                                                                                                                                               | Input Voltage<br>(Guaranteed | Operation Current<br>(Guaranteed  |

|----------|-----------------------------------------|--------------------|-----|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|

| Division |                                         | CH1                | CH2 |                                |                                                                                                                                                         | value)                       | value)                            |

|          | 4.7KΩ 1/4W                              |                    | 10  | Phase A pulse input            | At ON                                                                                                                                                   | 21.6 to 26.4V                | 2 to 5mA                          |

|          | <u>г</u>                                | 1                  | 19  | 24V                            | At OFF                                                                                                                                                  | 5V or less                   | 0.1mA or less                     |

|          | 2.2KΩ 1/4W                              |                    |     | Phase A pulse input            | At ON                                                                                                                                                   | 10.8 to 13.2V                | 2 to 5mA                          |

|          | •L                                      | 2                  | 20  | 12V                            | At OFF                                                                                                                                                  | 4V or less                   | 0.1mA or less                     |

|          | 470Ω 1/4W                               |                    |     | Phase A pulse input            | At ON                                                                                                                                                   | 4.5 to 5.5V                  | 2 to 5mA                          |

|          |                                         | 3                  | 21  | 5V                             | At OFF                                                                                                                                                  | 2V or less                   | 0.1mA or less                     |

|          | 5¥ ¥                                    | 4                  | 22  | СОМ                            |                                                                                                                                                         |                              |                                   |

| input    | 4.7KΩ 1/4W                              | _                  |     | Phase B pulse input            | At ON                                                                                                                                                   | 21.6 to 26.4V                | 2 to 5mA                          |

|          | ╎┎┫┛                                    | 5                  | 23  | 24V                            | At OFF                                                                                                                                                  | 5V or less                   | 0.1mA                             |

|          | 2.2KΩ 1/4W                              |                    |     | Phase B pulse input            | At ON                                                                                                                                                   | 10.8 to 13.2V                | 2 to 5mA                          |

|          |                                         | 6                  | 24  | 12V                            | At OFF                                                                                                                                                  | 4V or less                   | 0.1mA or less                     |

|          | 470Ω 1/4W                               |                    |     | Phase B pulse input            | At ON                                                                                                                                                   | 4.5 to 5.5V                  | 2 to 5mA                          |

|          |                                         | 7                  | 25  | 5V                             | At OFF                                                                                                                                                  | 2V or less                   | 0.1mA or less                     |

|          | 好                                       | 8                  | 26  | СОМ                            |                                                                                                                                                         |                              |                                   |

|          | 4.7KΩ 1/4W<br>680Ω 1/4W                 |                    |     | Disable input                  | At ON                                                                                                                                                   | 10.2 to 26.4V                | 2 to 6mA                          |

|          |                                         | 9                  | 27  | 12/24V                         | At OFF                                                                                                                                                  | 2V or less                   | 0.1mA or less                     |

| Input    |                                         |                    |     | Disable input                  | At ON                                                                                                                                                   | 4.5 to 5.5V                  | 3.5 to 5.5mA                      |

|          |                                         | 10                 | 28  | 5V                             | At OFF                                                                                                                                                  | 1.5V or less                 | 0.1mA or less                     |

|          | 5 × · · · · · · · · · · · · · · · · · · | 11                 | 29  | СОМ                            | Response<br>time                                                                                                                                        | OFF → ON<br>0.5ms or less    | ON → OFF<br>3ms or less           |

|          | 4.7KΩ 1/4W                              | 10                 |     | Preset input                   | At ON                                                                                                                                                   | 10.2 to 26.4V                | 2 to 6mA                          |

| ł        |                                         | 12                 | 30  | 12/24V                         | At OFF                                                                                                                                                  | 2V or less                   | 0.1mA or less                     |

| Input    | 680Ω 1/4W                               |                    |     | Preset input                   | At ON                                                                                                                                                   | 4.5 to 5.5V                  | 3.5 to 5.5mA                      |

|          |                                         | - 13               | 31  | 5V                             | At OFF                                                                                                                                                  | 1.5V or less                 | 0.1mA or less                     |

|          | 5×                                      | 14                 | 32  | СОМ                            | Response<br>time                                                                                                                                        | OFF → ON<br>0.5ms or less    | ON → OFF<br>3ms or less           |

|          | 8.2KΩ<br>//4W                           | 15                 | 33  | Open collector output<br>OUT   |                                                                                                                                                         |                              | IV<br>I Omsec                     |

| Output   |                                         | 16                 | 34  | ov                             | Maximum voltage drop at ON: 1.5V at 0.5A<br>Response time: OFF $\rightarrow$ ON 0.1msec or less<br>(Resistor load) ON $\rightarrow$ OFF 0.1msec or less |                              | I: 1.5V at 0.5A<br>.1msec or less |

|          | With varistor (52 to 62V)               | 17                 | 35  | 12/24V external<br>power input | Input voltage: 10.2 to 30V<br>Current consumption: 2 to 5mA                                                                                             |                              | mA                                |

# REMARKS

The AD61 accepts encoders in open collector output system and CMOS output system. Encoders in TTL output system and line driver output system are unavailable. When using an encoder in CMOS output system, check whether the output voltage of the encoder conforms to the D61S1 specifications.

#### 3. HANDLING

This chapter describes the handling instructions, nomenclature, maintenance, and inspection of the D61S1.

#### **3.1 Handling Instructions**

- (1) Protect the D61S1 and its terminal block from impact.

- (2) Do not touch or remove the printed circuit board from the case.

- (3) When wiring, ensure that no wire offcuts enter the unit and remove any that do enter.

- (4) Tighten terminal screws as specified below.

| Screw Location                               | Tightening Torque Range |  |  |

|----------------------------------------------|-------------------------|--|--|

| I/O terminal block terminal screw (M3 screw) | 49 to 78 N⋅m            |  |  |

| I/O terminal block mounting screw (M4 screw) | 78 to 137 N·m           |  |  |

| Unit mounting screw (M4 screw)               | 78 to 117 N⋅m           |  |  |

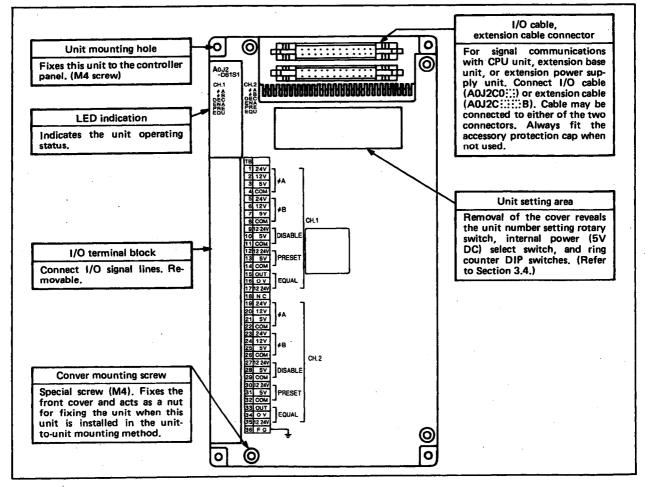

#### **3.2 Nomenclature and Explanation**

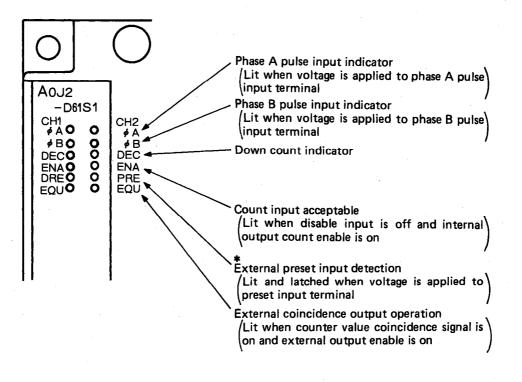

#### 3.3 LED Indicators

LED "on" conditions are explained below. LED operations of CH1 are the same as those of CH2.

#### REMARKS

\*If external preset detection reset signal (Y16 for CH1, Y1D for CH2) is turned on when this LED is on, it will turn off.

3-2

#### 3.4 Unit Setting Area Settings

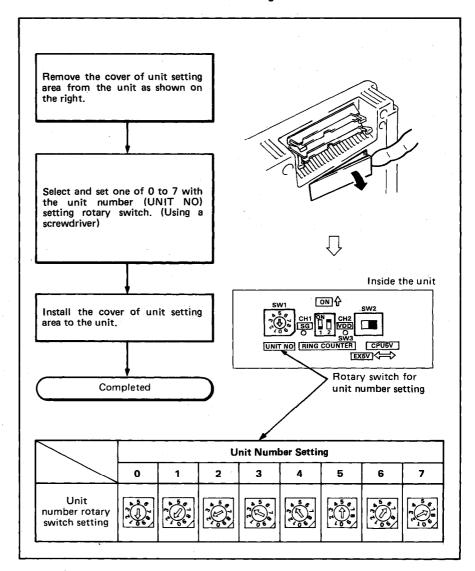

#### 3.4.1 Unit number setting

This section describes unit number setting.

## POINT

- (1) Set the rotary switch for unit number setting to an appropriate number in the range 0 to 7 according to the number of unit. Note that setting the same unit number between units causes input/output errors.

- (2) Setting of unit number determines X and Y addresses. For details, refer to Section 5.1 and 5.2.

#### 3.4.2 Ring counter function setting

Remove the unit setting area cover from the unit as shown on the right. Set whether the ring counter function is used or not with the RING COUNTER setting DIP switches. (When using the func-tion, set to ON. When not using the function, set to OFF.)  $\overline{\mathcal{O}}$ Inside the unit ⊡N₽ SW1 SW2 Install the setting area cover to the unit. VDD COUNTER CPU5V UNIT NO EX5V ( Ring counter function Completed setting DIP switches **Ring Counter Function Setting** CH1 Unused Used Unused Used CH2 Unused Unused Used Used Ring counter Π setting switches \*Black area indicates the slide switch position.

3-4

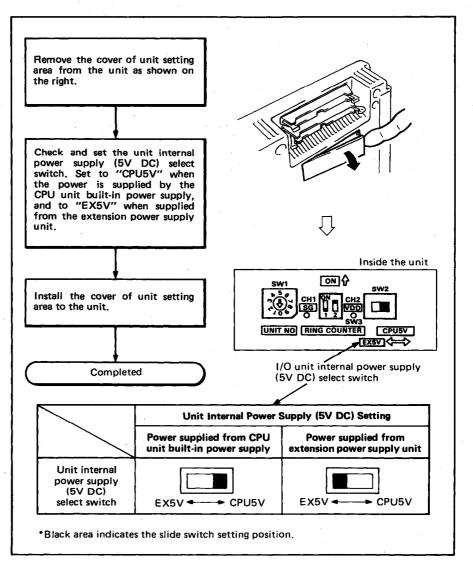

#### 3.4.3 Unit internal power supply (5V DC) setting

This section describes the setting of unit internal power supply (5V DC).

# POINT

- (1) If the select switch is set to EX5V when unit is supplied with 5V DC power by the CPU unit internal power supply, the unit does not operate properly. Be sure to check before the trial run.

- (2) To set the system using Type A0J2PW extension power supply unit, refer to the A0J2 CPU User's Manual (CPU Unit Edition).

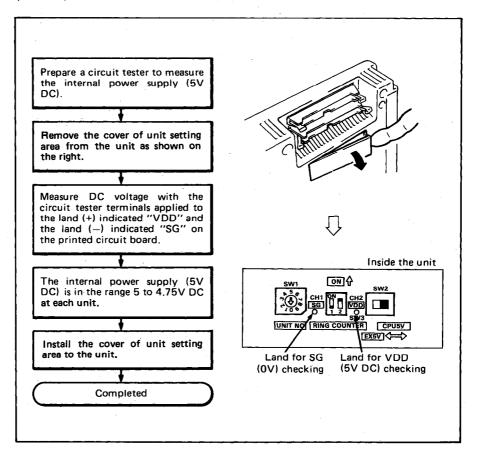

#### 3.4.4 Unit internal power supply (5V DC) check

This section describes how to check the unit internal power supply (5V DC). Use a circuit tester for measurement.

# POINT

The following switches are factory-set as described below:

Unit number setting switch ......0 Ring counter function setting switch ..... .....OFF (function unavailable) for CH1 and 2 Internal power setting switch ......CPU

# 4. WIRING AND INSTALLATION

#### 4. WIRING AND INSTALLATION

PC

Terminal

Terminal block

nverter

block

AC moto

#### 4.1 Wiring

4.1.1 Wiring instructions

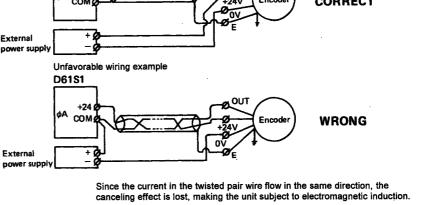

When using high speed pulse inputs take precautions against noise in all wiring.

- 1) Be sure to use shielded twisted pair wires. Also provide Class 3 grounding.

- 2) Do not run a twisted pair wire in parallel with any power line, I/O line, etc. which may generate noise. It is necessary to run the twisted pair wire separately from the above described lines and over the shortest possible distance.

- 3) A stabilized power supply is necessary for the pulse generated. For 1-phase input, connect count input signal only to phase A. For 2-phase input, connect count input signal to phase A and phase B.

Special care must be taken to prevent the input wiring from picking up noise. The diagram below indicates the type of precautions required.

D61S1

Metal piping. Never run solenoid or inductive wiring through the same conduit. If sufficient distance cannot be provided between the high current line and input wiring, use shielded wire for the high current line.

Joint box

Separate more than 15cm from equipment such as inverters, etc. (Also take care of wiring inside the panel.)

Carrier Encoder

Distance between encoder and joint box should be as short as possible. If the distance from the D61S1 to the encoder is too long an excessive voltage drop occurs. Therefore, measure the voltage during operation and check that the voltages are within the rated voltage of the encoder. If the voltage drop is large, increase the size of wiring or use an encoder of 24V DC with less current consumption.

•Ground twisted shield wire on the encoder side (joint box). (This is a connection example for 24V sink load.)

Connect the encoder shield wire to the twisted pair shield wire inside the joint box. If the shield wire of the encoder is not grounded in the encoder, ground it inside the joint box as indicated by dotted line.

#### 4.1.2 Unit wiring examples

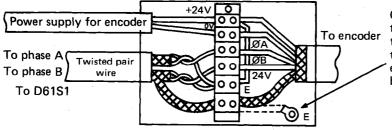

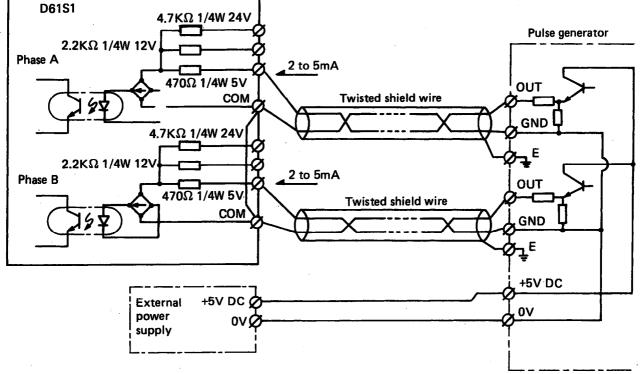

#### (1) Pulse generator is open collector output (24V DC)

4. WIRING AND INSTALLATION

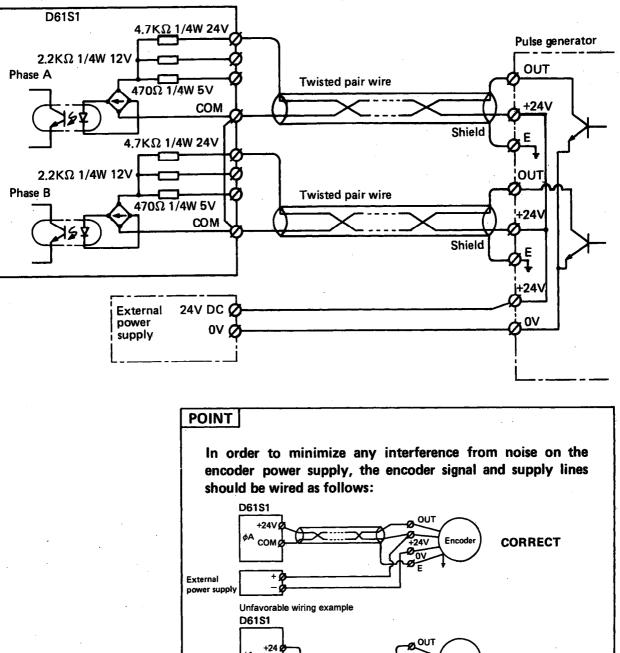

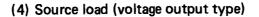

(2) Pulse generator is voltage output type (5V DC)

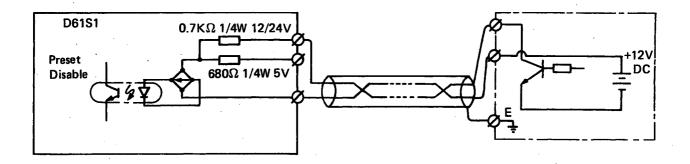

(3) Connection with input (the same interface for preset and disable)

4. WIRING AND INSTALLATION

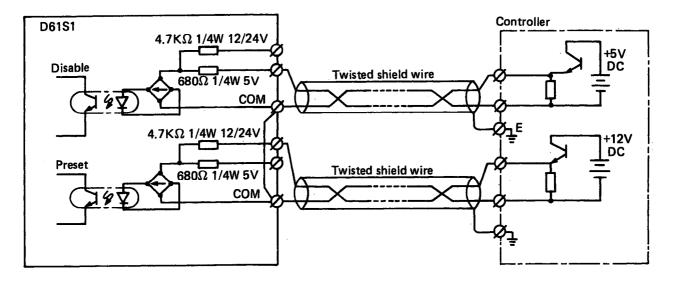

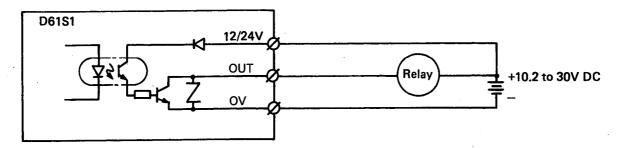

(5) Connection with EQU terminal

To use the EQU terminal, the internal photocoupler should be activated. For this purpose, 10.2 to 30V DC external power is necessary. The connection method is as follows:

4-4

#### 5. CONCEPT OF THE D61S1 I/O NUMBERS IN A0J2 SYSTEM

This chapter explains the concept and precautions for the D61S1 I/O numbers in the A0J2 system.

MELSEC-

#### 5.1 I/O Number Assignment and Concept

The I/O number assignment is one of the requirements for constructing a system. Wrong assignment will result in failure. Assign the I/O numbers as described below.

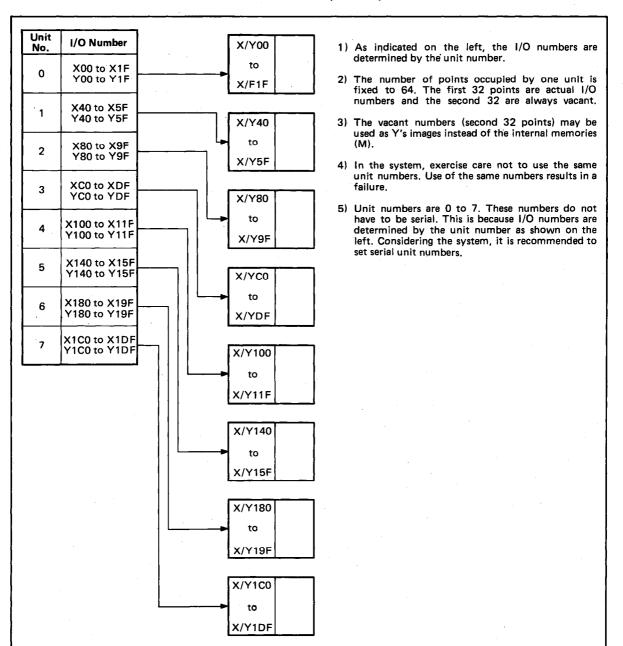

(1) X and Y represent inputs and outputs, respectively. I/O numbers are addressed in hexadecimal. (0 to F)

5-1

(2) I/O numbers are determined by the unit number set in the D61S1. One unit occupies 64 points.

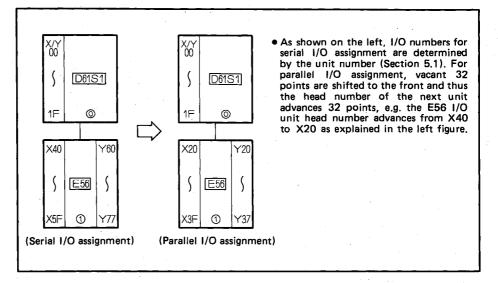

#### 5.2 Concept of Parallel I/O Assignment for Use with Remote Station

For the I/O number assignment in a remote station using the A0J2P25/ R25, serial and parallel I/O assignments are available. For details, refer to the A0J2 Data Link Unit User's Manual.

This section explains the precaution for parallel I/O assignment.

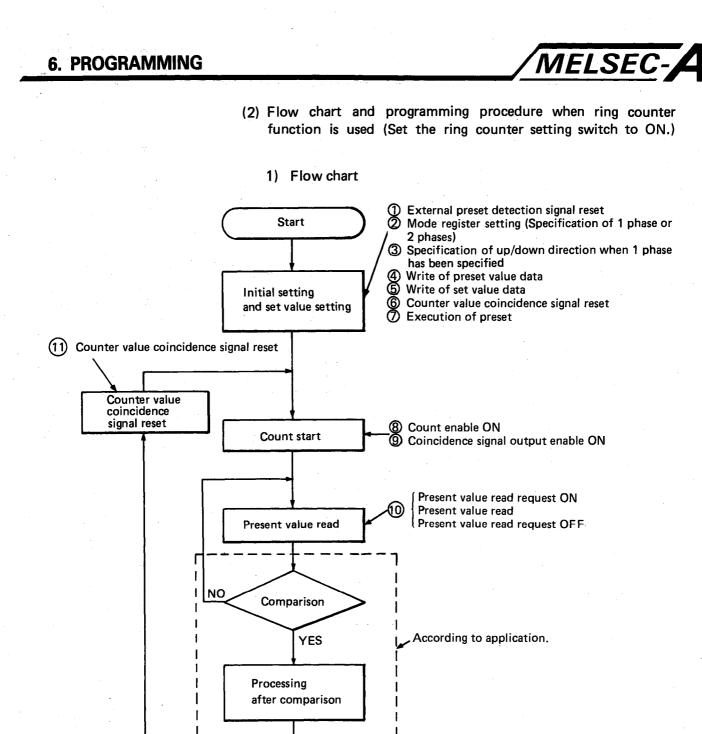

# 6. PROGRAMMING

6. PROGRAMMING This chapter explains the programming method necessary to use the D61S1.

#### 6.1 General Description of Programming

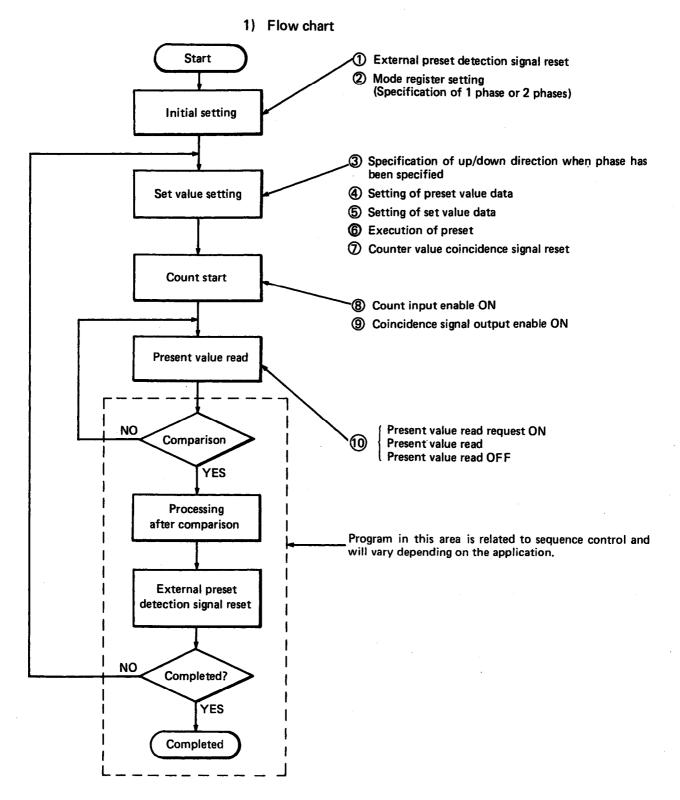

Program flow for the control of D61S1 is as shown below.

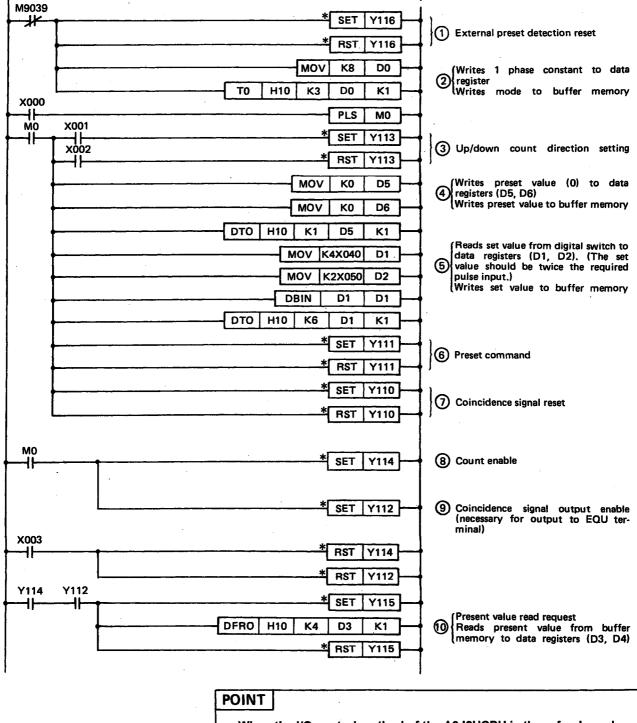

(1) Flow chart and programming procedure when ring counter function is not used (Set the ring counter setting switch to OFF.)

### 2) Programming procedure

The following example shows a programming procedure relevant to the flow chart in 1).

The D61S1 I/O numbers are assigned to 100 to 11F. This programming example is in the range (1) to (1)

When the I/O control method of the A0J2HCPU is the refresh mode, the SET/RST instructions cannot be used within the same scan as shown in the above \* marked ladder to output pulses to the D61S1. Use the partial refresh (SEG) instruction to output pulses to the D61S1.

Refer to the ACPU Programming Manual for the partial refresh (SEG) instruction.

### POINT

Completed?

Completed

YES

NO

When the ring counter function is used, the next preset cannot be performed if the counter coincidence signal (X01 for CH1, X05 for CH2) remains on. Be sure to reset the counter coincidence signal.

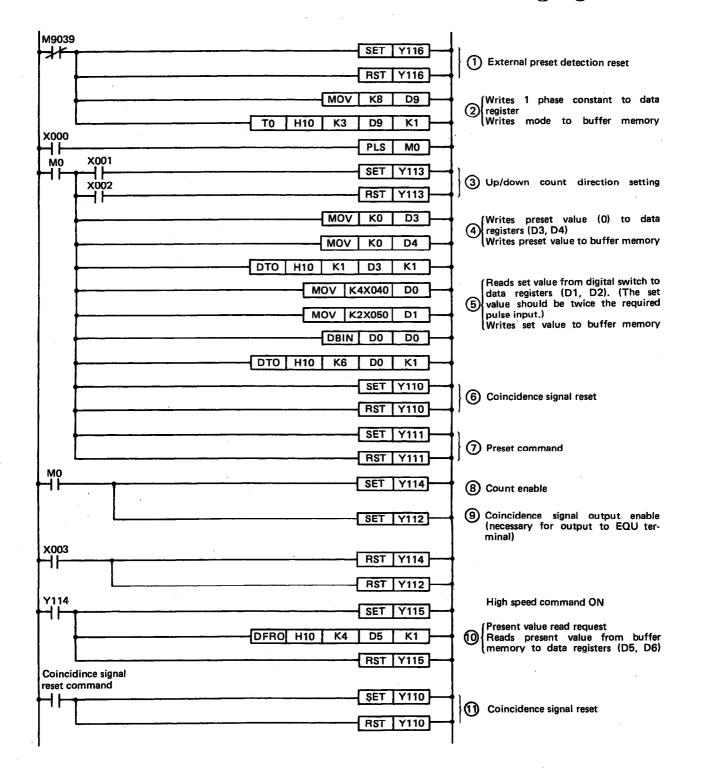

#### 2) Programming procedure

The following example shows a programming procedure relevant to the flow chart in 1).

The D61S1 I/O numbers are assigned to 100 to 11F. This programming example is in the range (1) to (1).

### (3) Differences of programming depending on system configurations

|                                                                                                                                                 | Instruction or Programming Method Necessary for Use of D61S1                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| System Configuration<br>Using AD61                                                                                                              | Accessing method to buffer<br>memory                                                                                                                                                            | D61S1 F/F reset pulse generating method                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| A0J2CPU independent system.<br>Data link system<br>(A0J2CPUP23/R23<br>local station).                                                           | FROM and TO instructions are used.                                                                                                                                                              | SET and RST are used.<br>Example:                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Data link system<br>(remote I/O station).<br>[Remote I/O station<br>(A0J2P25/R25) ac-<br>cessed by master<br>station (A1, A2,<br>A3CPUP21/R21)] | RFRP instruction<br>(equivalent to FROM instruc-<br>tion)<br>RTOP instruction<br>(equivalent to TO instruction)<br>Only one instruction may be<br>executed for 1 special unit<br>within 1 scan. | Since Y output to actual<br>remote I/O station is executed<br>after END of sequence pro-<br>gram, pulse is not output by<br>the above method.<br>To output pulse to remote I/O<br>station, create the following<br>program; SET Y16 $\rightarrow$ END<br>(link refresh) $\rightarrow$ RST Y16 $\rightarrow$<br>END (link refresh). |  |  |  |  |  |  |  |

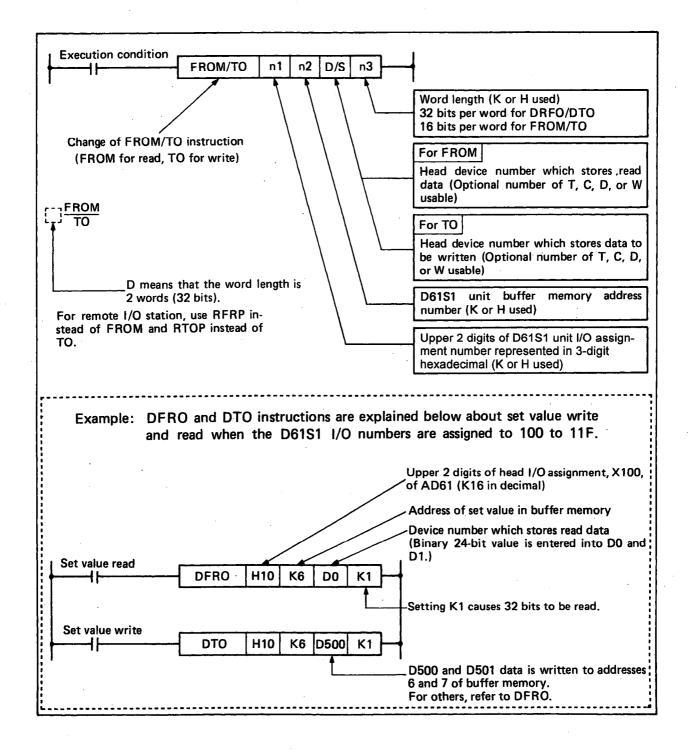

### 6.2 Programming

This section describes the programming procedure. Explanation will be given in order of programming flow chart in Section 6.1

To use any special function unit, utilize FROM and TO instructions. These instructions will be described below. For details, refer to the A0J2CPU and A1, A2, A3CPU Programming Manuals.

### (1) External preset detection reset

- input or preset by sequence program cannot be performed until the external preset flip flop has been reset.

- The external preset flip flop can be reset while the external preset input is on.

- o It is not necessary to execute this signal if the external preset terminal is not used.

(2) Setting of mode register (1-phase specification)

(3) Setting of mode register (2-phase specification)

(4) Setting of up/down count when 1-phase has been specified.

(5) Setting of preset value data (to set preset value to 100)

### POINT

A block diagram related to the preset operation of the D61S1 is shown below.

Three signals are available for preset operation.

- 1. Preset by program

- 2. Input from external preset terminal

- 3. Counter coincidence when ring counter is on

Preset operation uses logical add (OR) of these three signals. Upon rise of this signal from off to on, preset operation is performed. If one of the signals remains on, preset operation is not performed because, if another preset signal is turned from off to on, the output of logical add remains on. When ring counter function has been selected, counter value coincidence signal (preset signal) and external preset signal are latched by flip flop. Therefore, it is necessary to provide a reset signal to each of them.

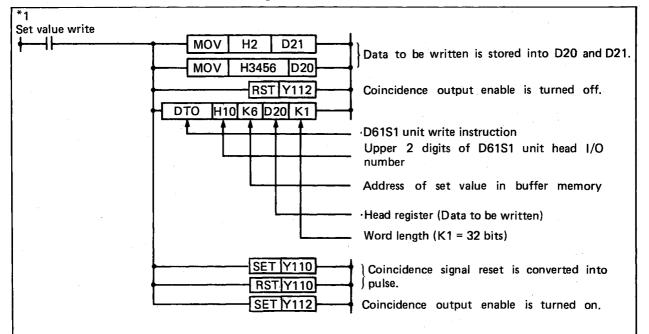

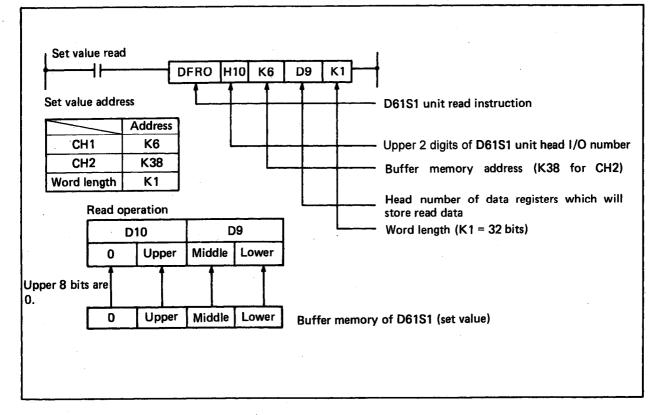

(6) Setting of set value data

Set value address and signal

|             | Address | Coincidence<br>output enable | Coincidence<br>signal reset |

|-------------|---------|------------------------------|-----------------------------|

| CH1         | K6      | Y112                         | Y110                        |

| CH2         | K38     | Y119                         | Y117                        |

| Word length |         | K1                           |                             |

• Convert the instruction marked \*1 into pulse.

•When external EQU terminal is not used, RST Y112 and SET Y112 are not required.

When the set value data is written to the buffer memory, the counter value coincidence signal may turn on. For this reason, turn off the coincidence output enable before the set value is written, reset the coincidence signal and finally re-enable the coincidence output.

(7) To reset coincidence signal

(8) To enable count input

#### (9) To enable coincidence signal output

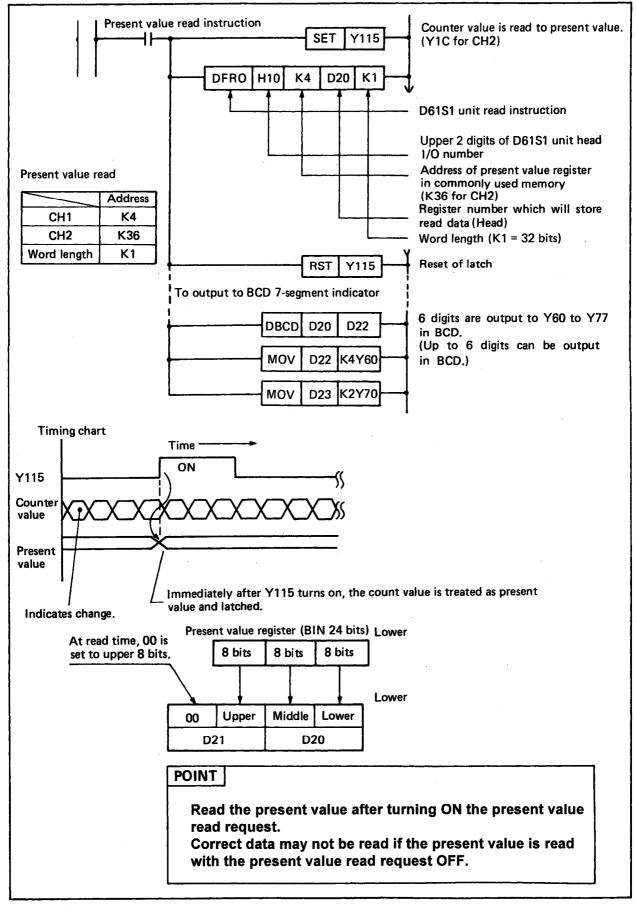

(10) Present value read

(11) Set value read

#### 6.3 Programming for Using the D61S1 in Remote I/O Station

This section explains programming for the master station (ACPU) when the D61S1 is loaded in a remote I/O station.

#### 6.3.1 Programming instructions

The ACPU I/O control method is a direct method. However, data communications to and from the remote I/O station are made in the batch refresh method after the END (FEND) instruction is executed. Hence, when the D61S1 is loaded in the remote I/O station, use care for the following points. For detailed data link specifications, refer to the Data Link Unit User's Manual.

- (1) Since control data between the master station CPU and remote I/O station D61S1 is controlled via the link unit, a time difference (response delay) occurs. Caution should be exercised for control timing.

- (2) For data communications with the D61S1 in the remote I/O station, use the following instructions:

Data write from the master station to the D61S1: RTOP instruction Data read from the D61S1 to the master station: RFRP instruction

Data communications between the master station CPU and D61S1 are made using the link registers (W). Therefore, create a processing program, as required, which transfers the link register contents to the other device after execution of the RFRP instruction or transfers data to be transferred to the link registers before execution of the RTOP instruction.

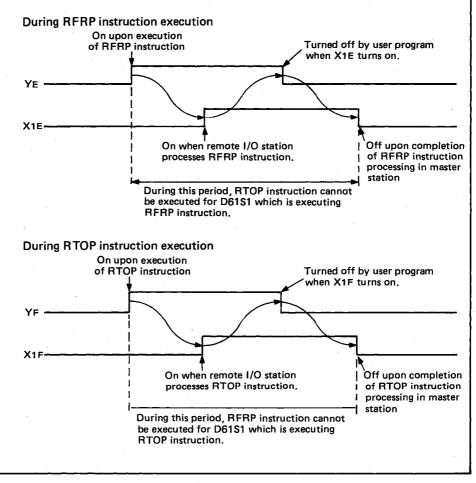

(3) The RTOP and RFRP instructions access from the master station to the remote I/O station. However, since these instructions cannot be executed during the same scan, always use interlock signals. For the interlocking procedure, refer to Fig. 6.1. For the programming procedure, refer to Section 6.3.2.

(4) Control signal to D61S1

- Because of the relation between the master station scan time and link scan time, Y and may not be output to the remote I/O station using PLS Y and.

- Since data communications between the master station and remote I/O station are made in the batch refresh method after execution of the END (FEND) instruction, pulse output which executes the RST instruction after the SET instruction execution cannot be used.

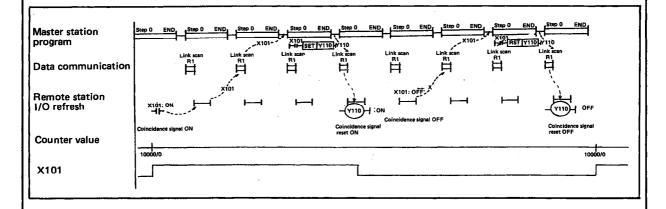

Several scans are required until all handshake signals are completed between the D61S1 and master station CPU. Caution should be exercised in the following example in which the counter coincidence signal (X01) is reset using the coincidence signal reset command (Y10). In this case, the D61S1 is assigned to a slot corresponding to the head I/O number X/Y100 and the set value is 10000. (The head I/O numbers of the master and remote I/O stations are X/Y100.)

In the above example, the counting time from 0 to the set value (10000) by the counter is longer than the handshake time between the D61S1 and PC CPU. Therefore, the D61S1 operates properly.

If the counting time is shorter than the handshake time (the set value is smaller than 10000 or the counting pulse frequency is greater), the D61S1 may misoperate or count a value greater than the set value.

In such a case, the D61S1 cannot be used in the remote I/O station. Therefore, load the D61S1 in the local station or use the COM instruction in the program. (For the COM instruction, refer to the Data Link Unit User's Manual.)

(Signal Direction) (Signal Direction) Master Station CPU to D61S1 D61S1 to Master Station CPU Device Device Signal Signal No. No. X10 Yo Unusable, Unusable. to YD to X1D On at RFRP instruction execu-On while the remote I/O station tion. is processing the RFRP instruc-YΕ X1E To be reset by user program after tion. checking that X1E is on. On at RTOP instruction execu-On while the remote 1/O station tion. YF X1F is processing the RTOP instruc-To be reset by user program after checking that X1F is on. tion.

- 6-17 -

| Format |                                                                    | . [                 |  |  |  |  |  |  |

|--------|--------------------------------------------------------------------|---------------------|--|--|--|--|--|--|

| Exec   | PFRP n1 n2 D n                                                     | 3                   |  |  |  |  |  |  |

|        |                                                                    |                     |  |  |  |  |  |  |

| Symbol | Description                                                        | Available<br>Device |  |  |  |  |  |  |

| n1     | Head 3 digits of the D61S1 I/O number assigned from master station |                     |  |  |  |  |  |  |

| n2     | Head address of D61S1 buffer memory which stores data to be read   |                     |  |  |  |  |  |  |

| D      | Head number of link registers which will store read data W         |                     |  |  |  |  |  |  |

| n3     | Number of data to be read                                          |                     |  |  |  |  |  |  |

MELSEC-

#### (1) Read from remote I/O station D61S1

Example: To read two words from the buffer memory addresses 4 and 5 (present value) in the remote I/O station D61S1, corresponding to X, Y130 to 14F assigned from the master station, to W50 and W51.

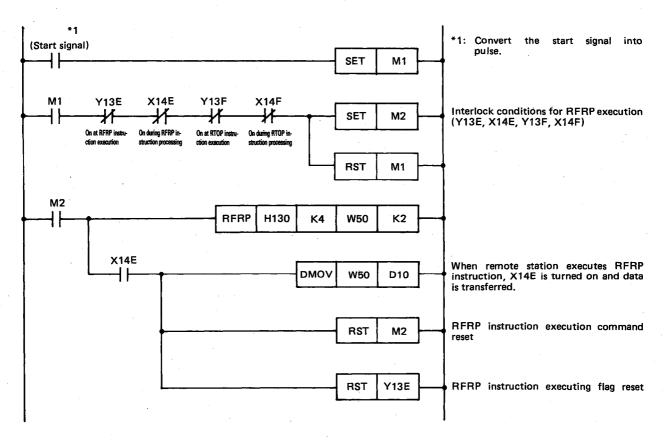

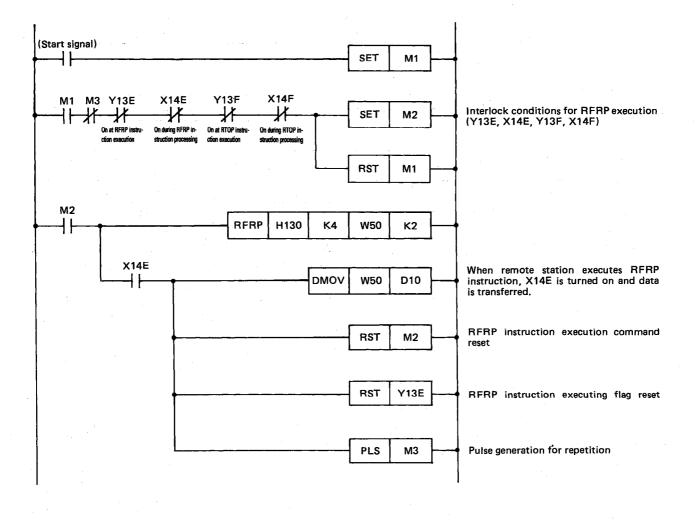

To execute only once by turning on the start signal

To keep executing while the start signal is on

### POINT

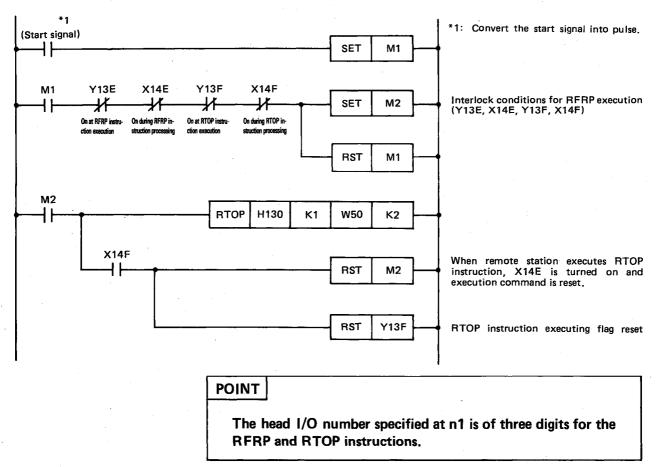

The head I/O number specified at n1 is of three digits for the RFRP and RTOP instructions.

(2) Write to remote I/O station D61S1

| Format<br>Execu | tion condition RTOP n1 n2 D n                                      | 3                   |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------|---------------------|--|--|--|--|--|--|

| Symbol          | Description                                                        | Available<br>Device |  |  |  |  |  |  |

| n1              | Head 3 digits of the D61S1 I/O number assigned from master station |                     |  |  |  |  |  |  |

| n2              | Head address of D61S1 buffer memory to which data will be written  |                     |  |  |  |  |  |  |

| D               | Head number of link registers which store data to be written       |                     |  |  |  |  |  |  |

| n3              | Number of data to be written                                       | к, н                |  |  |  |  |  |  |

Example: To write two words from link registers, beginning with W50, to the buffer memory addresses 1 and 0 (preset value) in the remote I/O station D61S1 corresponding to X, Y130 to 14F assigned from the master station.

To execute only once by turning on the start signal

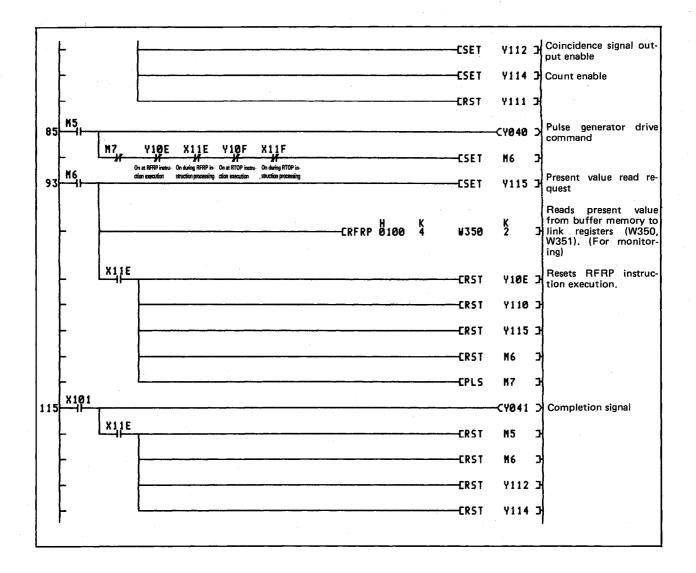

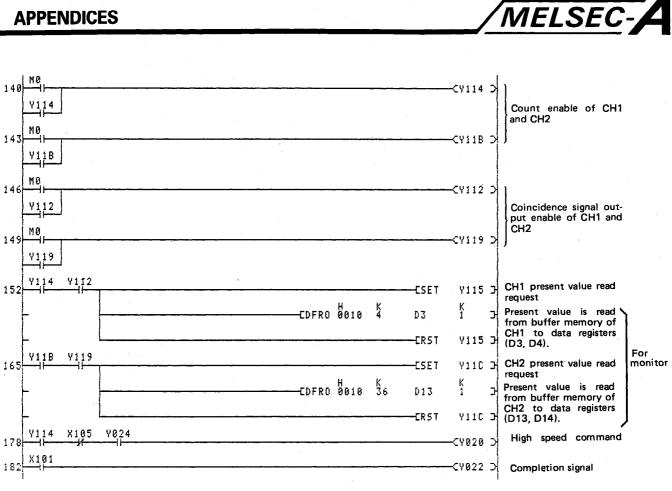

#### 6.3.3 Program example

The following program monitors a present value with the D61S1 loaded in the remote I/O station. Conditions are as follows:

- (1) The D61S1 has been assigned to X/Y100 to 11F from the master station.

- (2) Link registers used are W320 to 33F (32 points) for the RTOP instruction and W350 to W36F (32 points) for the RFRP instruction.

- (3) Device assignment

W330, W331: preset value, W332: mode, W333, W334: set value, W350, W351: present value, X0: start command, Y40: pulse generator drive command, Y41: completion signal

|    | M9039     |                                     |                                                                                                                | K       |        | _1                                                      |                     |

|----|-----------|-------------------------------------|----------------------------------------------------------------------------------------------------------------|---------|--------|---------------------------------------------------------|---------------------|

| 0  |           |                                     |                                                                                                                |         |        | Writes present<br>link registers                        | value to (W330,     |

|    | -         |                                     |                                                                                                                | Ø ·     | ₩331   | W331).                                                  |                     |

|    | -         |                                     |                                                                                                                | K<br>18 | ₩332   | Writes 2-phase to link register                         | constant<br>(W332). |

| 16 | X000      |                                     |                                                                                                                | -CPLS   | N10    | Contemporal Start signal                                |                     |

| 20 | H10       |                                     |                                                                                                                | -CSET   | M 1    | Э                                                       |                     |

| 22 |           | <u> 10е</u><br>И                    |                                                                                                                | -CSET   | M2     | Э                                                       |                     |

|    | ctior     | t RFRP instru- On<br>execution stru | string RFRP in- On at RTOP instru- On during RTOP in-<br>ction processing ction execution struction processing | -CRST   | MÌ     | Reads set value<br>register (W333,<br>(For set value, s | W334).              |

| 29 | N2<br>    |                                     |                                                                                                                |         | ₩333   |                                                         | s greater           |

|    | -         |                                     |                                                                                                                | -CSET   | Y116   | External preset                                         | detec-              |

|    | -         |                                     | CRTOP 0100 1                                                                                                   | W330    | K<br>3 | Writes preset va<br>mode to buffer<br>ry.               |                     |

|    |           |                                     |                                                                                                                | -CRST   | Y 10F  |                                                         | instruc-            |

|    | ┝         |                                     |                                                                                                                | -CRST   | M2     | Э.                                                      |                     |

|    |           |                                     |                                                                                                                | -CSET   | M3     | Z                                                       |                     |

|    | <b>–</b>  |                                     | X103                                                                                                           | -CRST   | Y116   | J .                                                     |                     |

| 57 | H3<br>0na | Y 10E                               | X11E Y10F X11F                                                                                                 | -ESET I | M4     | Э                                                       | ·                   |

|    |           |                                     | ction processing ction execution struction processing                                                          | -CRST I | M 3    | 2                                                       |                     |

| 64 | N4<br>    |                                     |                                                                                                                | W333    | K<br>2 | Writes set va<br>buffer memory.                         | lue to              |

|    | -         |                                     |                                                                                                                | -CSET . | Y111   | Preset command                                          | ·                   |

|    | _         | X11F                                |                                                                                                                | ERST    | Y 10 F | Resets RTOP                                             | instruc-            |

|    | -         |                                     |                                                                                                                | ERST I  | 44     | z                                                       |                     |

|    | -         |                                     |                                                                                                                | ESET N  | 15     | Э                                                       |                     |

|    | -         |                                     |                                                                                                                | CSET Y  | Y110   | Coincidence sigr                                        | al reset            |

|    |           |                                     |                                                                                                                | _       |        |                                                         |                     |

MELSEC

# 7. TEST OPERATION

### 7. TEST OPERATION

#### 7.1 Pre-test Checks

### IMPORTANT

Before switching on the encoder power supply, check that the correct terminals have been used. Application of 24V to 5V terminals will damage the unit.

MELSEC-

Before turning on the power, check the following:

- 1. Ring counter setting switch.

- 2. Check that the D61S1 cable is properly connected.

- 3. Check terminal wiring.

- 4. Check the voltage of the external power supply.

After the above checks, turn on the power and operate the pulse generator. Check the relevant phase indicator LED.

### 8. TROUBLESHOOTING

This chapter explains troubleshooting procedures for the D61S1. For the CPU unit, refer to the A0J2 Programming Manual.

### 8.1 General Troubleshooting Flow Chart

### 8.2 Flow Chart Used When Phase A(B) Pulse Input LED Does Not Flicker

### 8.3 Flow Chart Used When D61S1 Does Not Count

IB (NA) 66094-A

#### 8.4 Flow Chart When Count Value Is Incorrect

IB (NA) 66094-A

APPENDIX 1 Application Circuit Examples

- Example of turn table indexing

- Example using ring counter function

- Example using CH1 and CH2 coincidence signal output

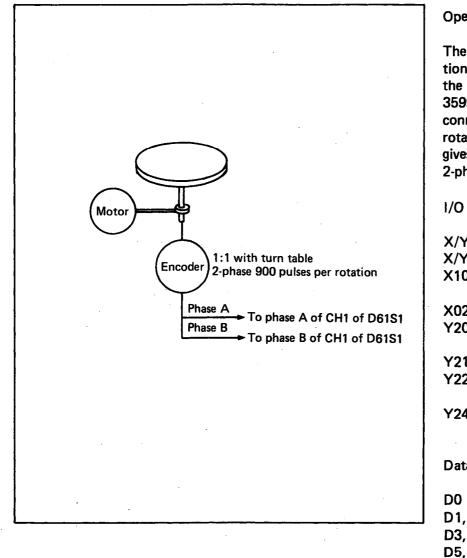

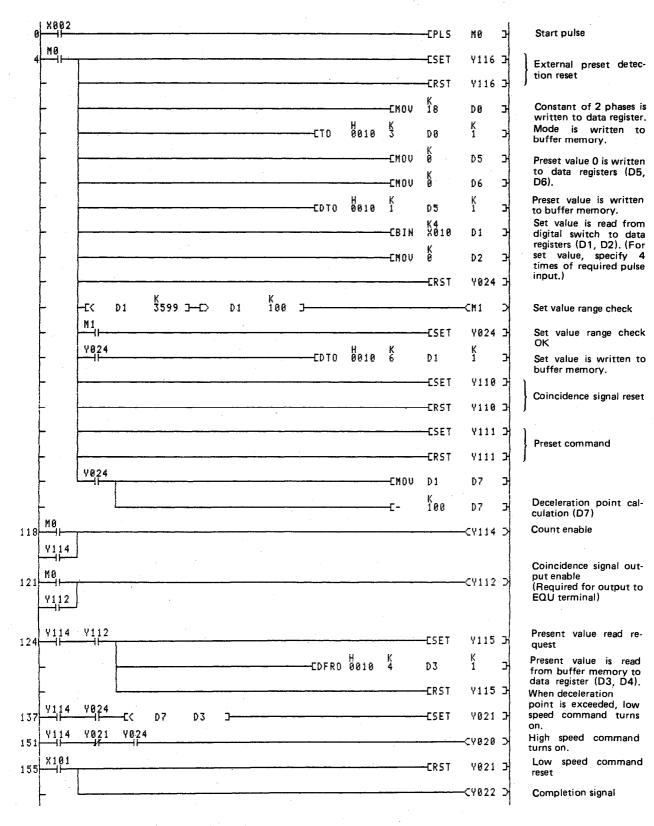

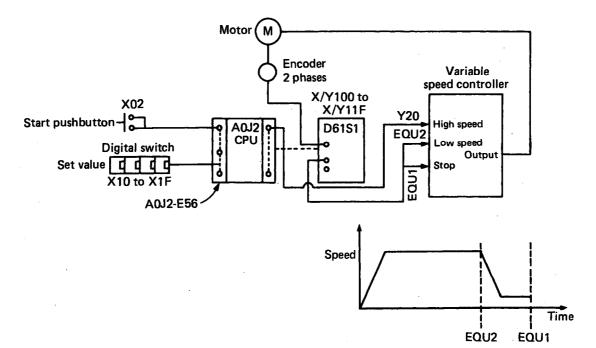

(1) Example of turn table indexing

#### Operation

The indexing table is positioned at a corresponding to the digital switch setting (0 to 3599). The encoder is directly connected to the turn table rotating shaft. The encoder gives 900 pulses per rotation, 2-phase.

I/O assignment

| X/Y100 to<br>X/Y11F | D61S1             |

|---------------------|-------------------|

| X10 to X1F          | 4 digits of digi- |

|                     | tal switch        |

| X02                 | Start switch      |

| Y20                 | Motor high        |

|                     | speed             |

| Y21                 | Motor low speed   |

| Y22                 | Completion        |

|                     | signal            |

| Y24                 | Set value range   |

|                     | ОК                |

| Data register       | assignment        |

| D0                  | Mode              |

| D1, D2              | Set value         |

|                     |                   |

| D2 | Set value     |

|----|---------------|

| D4 | Present value |

| D6 | Preset value  |

|    | Deceleration  |

|    | point value   |

When the start pushbutton is pressed, the motor rotates at high speed and present the value is read. 10 degrees ahead of the indexing point, the speed is reduced. When the counter value coincidence signal turns on, the turn table is brought to a stop. (If the set value is 10 degrees (100 counts) or less, the program does not operate.)

**D7**

#### Example of turn table indexing

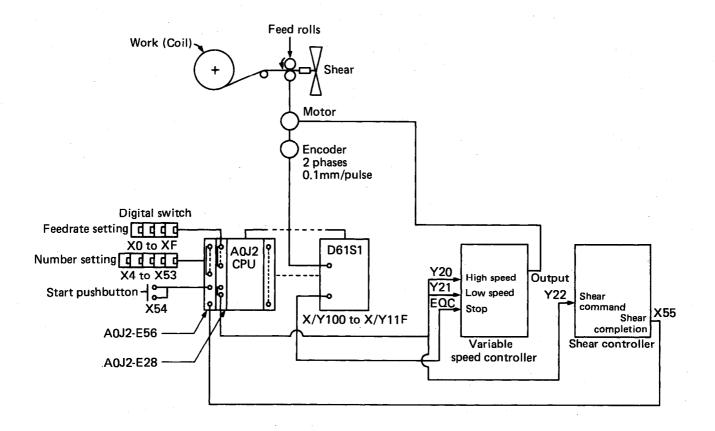

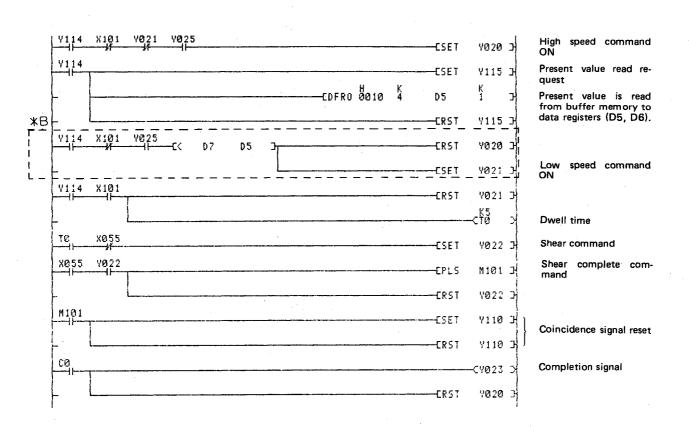

(2) Example using ring counter function

Shearing control application using the ring counter function. (Set the ring counter setting switch to ON.)

#### Operation

When the start pushbutton is pressed, the amount set by the feedrate digital switch is advanced. When positioning is completed, a shear command is sent to the shear controller. When shearing is complete, the positioning operation is repeated. (Deceleration point is 100 counts ahead of the set value. If the set value is 100 counts or less, the program does not operate.)

In this case, assume that the D61S1 is assigned to X/Y100 to X/Y11F.

Data register assignment

| D0, D1 | Set value          |

|--------|--------------------|

| D2     | Number value       |

| D3, D4 | Preset value       |

| D5, D6 | Present value      |

| D7, D8 | Deceleration point |

| D9     | Mode               |

Operation timing (Number setting = 2) Start pushbutton High speed Low speed Stop Stop Shear completion

### (A) Programming example when set value is 32767 or less

|                    | 1 ¥114               |    |          | <br><del></del> |                                       |           |            | EPLS         | M100             | Э                     | Start pulse                                                                       |

|--------------------|----------------------|----|----------|-----------------|---------------------------------------|-----------|------------|--------------|------------------|-----------------------|-----------------------------------------------------------------------------------|

| M100               |                      |    |          | <br>            |                                       |           |            | CSET         | Y116             | 거                     | External preset detec                                                             |

| <u> </u>           |                      |    |          | <br>            |                                       |           |            | ERST         | Y116             | Ę                     | tion reset                                                                        |

|                    |                      |    |          |                 |                                       |           | -EMOV      | К<br>18      | D 9              | Н                     | Constant of 2 phases i written to data register                                   |

| <b>_</b>           |                      |    |          | <br>            | ETO                                   | H<br>0010 | K<br>3     | D 9          | K<br>1           | Э                     | Mode is written to buf<br>er memory.                                              |

| -                  |                      |    |          |                 |                                       |           | -CMOV      | С<br>К       | D 3              | Э                     | Preset value 0 is writte                                                          |

| -                  |                      |    |          | <br>            | · · ·                                 |           | -CNOV      | K<br>Ø       | D 4              | ]                     | to data registers (D3<br>D4).                                                     |

|                    |                      |    |          | <br><del></del> |                                       |           | -CMOV      | K 4<br>XØ 40 | DØ               | н<br>Э                | Set value is read from                                                            |

| _                  |                      |    |          | <br><u> </u>    |                                       |           | -EMOU      | K 1<br>XØ 50 | D 1              |                       | digital switch to data<br>registers (D0, D1). (Fo<br>set value, specify 4         |